Porte logiche CD74HCT86M96 Quad Hi Spd 2 ingressi

♠ Descrizione del prodotto

| Attributo del prodotto | Valore dell'attributo |

| Produttore: | Texas Instruments |

| Categoria di prodotto: | Porte logiche |

| Direttiva RoHS: | Dettagli |

| Prodotto: | Cancello monofunzione |

| Funzione logica: | XOR |

| Famiglia logica: | trapianto di cellule staminali |

| Numero di porte: | 4 Cancello |

| Numero di linee di input: | 2 Ingresso |

| Numero di linee di uscita: | 1 Uscita |

| Corrente di uscita ad alto livello: | - 5,2 mA |

| Corrente di uscita di basso livello: | 5,2 mA |

| Tempo di ritardo di propagazione: | 40 ns |

| Tensione di alimentazione - Max: | 5,5 V |

| Tensione di alimentazione - Min: | 4,5 V |

| Temperatura minima di esercizio: | - 55 gradi Celsius |

| Temperatura massima di esercizio: | + 125 °C |

| Stile di montaggio: | SMD/SMT |

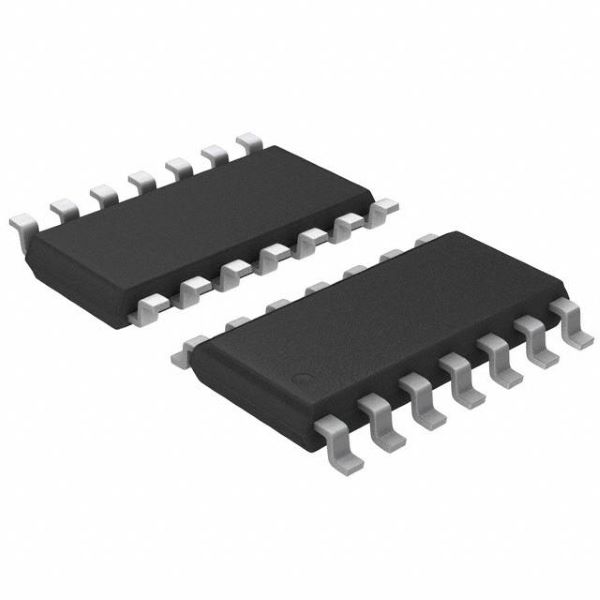

| Confezione/custodia: | SOIC-14 |

| Confezione: | Bobina |

| Confezione: | Tagliare il nastro |

| Confezione: | MouseReel |

| Marca: | Texas Instruments |

| Funzione: | Quad Hi Spd 2 Input |

| Altezza: | 1,58 millimetri |

| Tipo di input: | Tempo di esecuzione |

| Lunghezza: | 8,65 millimetri |

| Tipo di logica: | 2-Input Esclusivo-OR |

| Numero di bit: | 4 bit |

| Corrente di alimentazione operativa: | 20 µA |

| Tensione di alimentazione operativa: | 5 Volt |

| Intervallo di temperatura di funzionamento: | - 55 °C a + 125 °C |

| Tipo di output: | CMOS |

| Tipo di prodotto: | Porte logiche |

| Serie: | CD74HCT86 |

| Quantità confezione di fabbrica: | 2500 |

| Sottocategoria: | Circuiti integrati logici |

| Larghezza: | 3,91 millimetri |

| Peso unitario: | 129.400 mg |

♠ CDx4HCT86 Porte XOR quadruple a 2 ingressi

Questo dispositivo contiene quattro porte XOR indipendenti a 2 ingressi. Ogni porta esegue la funzione booleana Y = A ⊕ B in logica positiva.

• Compatibile con la logica di ingresso LSTTL

– VIL(max) = 0,8 V, VIH(min) = 2 V

• Compatibile con la logica di ingresso CMOS

– II ≤ 1 µA a VOL, VOH

• Ingressi bufferizzati

• Funzionamento da 4,5 V a 5,5 V

• Ampio intervallo di temperatura di funzionamento: da -55°C a +125°C

• Supporta fanout fino a 10 carichi LSTTL

• Riduzione significativa della potenza rispetto ai circuiti integrati logici LSTTL

• Rilevare le differenze di fase nei segnali di ingresso

• Creare un inverter/buffer selezionabile