TMS320C6674ACYPA Multicore Fix/Float Pt Dig Sig Proc

♠ Descrizione del prodotto

| Attributo del prodotto | Valore dell'attributo |

| Produttore: | Texas Instruments |

| Categoria di prodotto: | Processori e controllori di segnale digitale - DSP, DSC |

| Prodotto: | DSP |

| Serie: | TMS320C6674 |

| Stile di montaggio: | SMD/SMT |

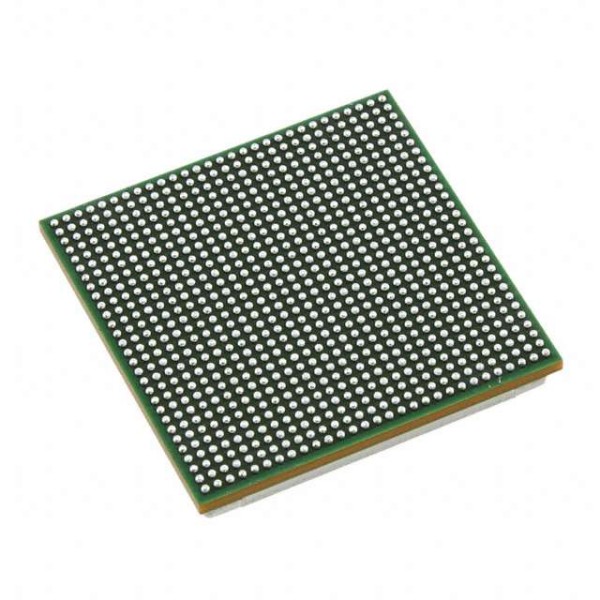

| Confezione/custodia: | FCBGA-841 |

| Nucleo: | C66x |

| Numero di core: | 4 Nuclei |

| Frequenza di clock massima: | 1 GHz, 1,25 GHz |

| Memoria istruzioni cache L1: | 4 x 32 kB |

| Memoria dati cache L1: | 4 x 32 kB |

| Dimensione della memoria del programma: | - |

| Dimensione RAM dati: | - |

| Tensione di alimentazione operativa: | Da 900 mV a 1,1 V |

| Temperatura minima di esercizio: | - 40 °C |

| Temperatura massima di esercizio: | + 100 °C |

| Confezione: | Vassoio |

| Marca: | Texas Instruments |

| Larghezza del bus dati: | 8 bit/16 bit/32 bit |

| Tipo di istruzione: | Punto fisso/mobile |

| MMACS: | 160000 MMACS |

| Sensibile all'umidità: | SÌ |

| Numero di I/O: | 16 I/O |

| Numero di timer/contatori: | 12 Timer |

| Tipo di prodotto: | DSP - Processori e controllori di segnale digitale |

| Quantità confezione di fabbrica: | 44 |

| Sottocategoria: | Processori e controller integrati |

| Tensione di alimentazione - Max: | 1,1 V |

| Tensione di alimentazione - Min: | 900 mV |

| Peso unitario: | 0,173396 once |

♠ Processore di segnale digitale multicore a virgola fissa e mobile

Il DSP TMS320C6674 è un DSP a virgola fissa/mobile ad altissime prestazioni basato sull'architettura multicore KeyStone di TI. Incorporando il nuovo e innovativo core DSP C66x, questo dispositivo può raggiungere una velocità di clock fino a 1,25 GHz. Per gli sviluppatori di un'ampia gamma di applicazioni, come sistemi mission-critical, imaging medicale, test e automazione e altre applicazioni che richiedono prestazioni elevate, il DSP TMS320C6674 di TI offre una potenza DSP cumulativa di 5 GHz e abilita una piattaforma efficiente dal punto di vista energetico e facile da usare. Inoltre, è completamente retrocompatibile con tutti i DSP a virgola fissa e mobile della famiglia C6000 esistenti.

L'architettura KeyStone di TI fornisce una piattaforma programmabile che integra vari sottosistemi (core C66x, sottosistema di memoria, periferiche e acceleratori) e utilizza diversi componenti e tecniche innovative per massimizzare la comunicazione intra-dispositivo e inter-dispositivo, consentendo alle varie risorse DSP di operare in modo efficiente e senza interruzioni. Al centro di questa architettura vi sono componenti chiave come Multicore Navigator, che consente una gestione efficiente dei dati tra i vari componenti del dispositivo. TeraNet è una struttura di commutazione non bloccante che consente uno spostamento interno dei dati rapido e senza conflitti. Il controller di memoria condivisa multicore consente l'accesso diretto alla memoria condivisa ed esterna senza attingere alla capacità della struttura di commutazione.

• Quattro sottosistemi core DSP TMS320C66x™ (C66x CorePacs), ciascuno con

– Core CPU a virgola fissa/mobile C66x da 1,0 GHz o 1,25 GHz

› 40 GMAC/Core per punto fisso a 1,25 GHz

› 20 GFLOP/core per virgola mobile a 1,25 GHz

– Memoria

› 32K Byte L1P per core

› 32K Byte L1D per core

› 512 K Byte L2 locale per core

• Controller di memoria condivisa multicore (MSMC)

– Memoria SRAM MSM da 4096 KB condivisa da quattro DSP C66x CorePac

– Unità di protezione della memoria per MSM SRAM e DDR3_EMIF

• Navigatore multicore

– 8192 code hardware multiuso con gestore code

– DMA basato su pacchetti per trasferimenti senza overhead

• Coprocessore di rete

– L’acceleratore di pacchetti consente il supporto per

› Piano di trasporto IPsec, GTP-U, SCTP, PDCP

› Piano utente L2 PDCP (RoHC, cifratura aerea)

› Velocità di trasmissione dati wire-speed di 1 Gbps a 1,5 Mpacchetti al secondo

– Il motore di accelerazione della sicurezza consente il supporto per

› Sicurezza IPSec, SRTP, 3GPP, WiMAX Air Interface e SSL/TLS

› ECB, CBC, CTR, F8, A5/3, CCM, GCM, HMAC, CMAC, GMAC, AES, DES, 3DES, Kasumi, SNOW 3G, SHA-1, SHA-2 (hash a 256 bit), MD5

› Velocità di crittografia fino a 2,8 Gbps

• Periferiche

– Quattro corsie di SRIO 2.1

› Operazione da 1,24/2,5/3,125/5 GBaud supportata per corsia

› Supporta I/O diretto, passaggio di messaggi

› Supporta quattro configurazioni di collegamento 1×, due 2×, una 4× e due 1× + una 2×

– PCIe Gen2

› Porta singola che supporta 1 o 2 corsie

› Supporta fino a 5 GBaud per corsia

– Collegamento ipertestuale

› Supporta connessioni ad altri dispositivi con architettura KeyStone, garantendo scalabilità delle risorse

› Supporta fino a 50 Gbaud

– Sottosistema di commutazione Gigabit Ethernet (GbE)

› Due porte SGMII

› Supporta il funzionamento a 10/100/1000 Mbps

– Interfaccia DDR3 a 64 bit (DDR3-1600)

› Spazio di memoria indirizzabile da 8 GB di byte

– EMIF a 16 bit

– Due porte seriali per telecomunicazioni (TSIP)

› Supporta 1024 DS0 per TSIP

› Supporta 2/4/8 corsie a 32,768/16,384/8,192 Mbps per corsia

– Interfaccia UART

– Interfaccia I²C

– 16 pin GPIO

– Interfaccia SPI

– Modulo Semaforo

– Dodici timer a 64 bit

– Tre PLL on-chip

• Temperatura commerciale:

– da 0°C a 85°C

• Temperatura estesa:

– da -40°C a 100°C

• Sistemi critici per la missione

• Sistemi di calcolo ad alte prestazioni

• Comunicazioni

• Audio

• Infrastruttura video

• Imaging

• Analisi

• Networking

• Elaborazione dei media

• Automazione industriale

• Automazione e controllo dei processi