Processori e controllori di segnale digitale TMS320F2812PGFA DSP DSC Controller di segnale digitale a 32 bit con flash

♠ Descrizione del prodotto

| Attributo del prodotto | Valore dell'attributo |

| Produttore: | Texas Instruments |

| Categoria di prodotto: | Processori e controllori di segnale digitale - DSP, DSC |

| Direttiva RoHS: | Dettagli |

| Prodotto: | DSC |

| Serie: | TMS320F2812 |

| Nome commerciale: | C2000 |

| Stile di montaggio: | SMD/SMT |

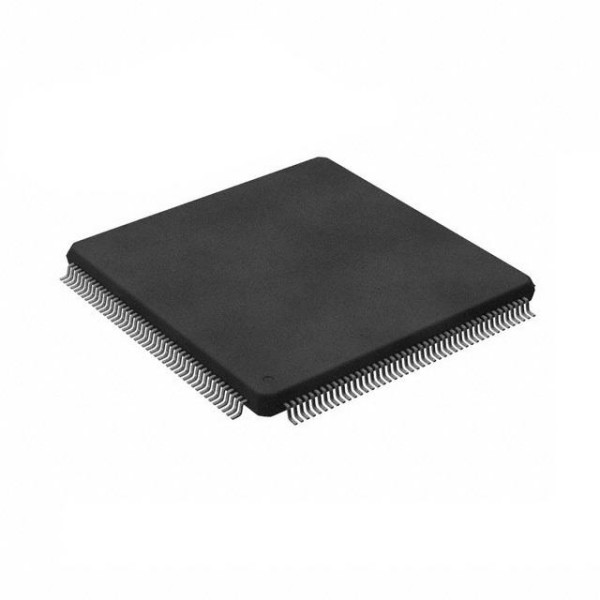

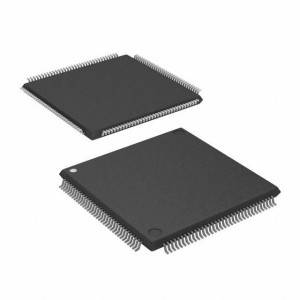

| Confezione/custodia: | LQFP-176 |

| Nucleo: | C28x |

| Numero di core: | 1 Nucleo |

| Frequenza di clock massima: | 150 MHz |

| Memoria istruzioni cache L1: | - |

| Memoria dati cache L1: | - |

| Dimensione della memoria del programma: | 256 kB |

| Dimensione RAM dati: | 36 kB |

| Tensione di alimentazione operativa: | 1,9 V |

| Temperatura minima di esercizio: | - 40 °C |

| Temperatura massima di esercizio: | + 125 °C |

| Confezione: | Vassoio |

| Risoluzione ADC: | 12 bit |

| Marca: | Texas Instruments |

| Larghezza del bus dati: | 32 bit |

| Tensione I/O: | 3,3 V |

| Tipo di istruzione: | Punto fisso |

| Sensibile all'umidità: | SÌ |

| Tipo di prodotto: | DSP - Processori e controllori di segnale digitale |

| Quantità confezione di fabbrica: | 40 |

| Sottocategoria: | Processori e controller integrati |

| Peso unitario: | 0,066886 once |

• Tecnologia CMOS statica ad alte prestazioni

– 150 MHz (tempo di ciclo 6,67 ns)

– Basso consumo energetico (core da 1,8 V a 135 MHz,Core da 1,9 V a 150 MHz, progettazione 3,3-VI/O)

• Supporto per la scansione dei confini JTAG

– Standard IEEE 1149.1-1990 Standard IEEEPorta di accesso di prova e Boundary-ScanArchitettura

• CPU a 32 bit ad alte prestazioni (TMS320C28x)

– Operazioni MAC 16 × 16 e 32 × 32

– 16 × 16 doppio MAC

– Architettura degli autobus di Harvard

– Operazioni atomiche

– Risposta e elaborazione rapide agli interrupt

– Modello di programmazione della memoria unificato

– Portata dell'indirizzo di programma/dati lineare 4M

– Codice efficiente (in C/C++ e Assembly)

– Codice sorgente del processore TMS320F24x/LF240xcompatibile

• Memoria on-chip

– Fino a 128K × 16 flash(Quattro settori da 8K × 16 e sei da 16K × 16)

– ROM OTP da 1K × 16

– L0 e L1: 2 blocchi da 4K × 16 ciascuno SingleAccess RAM (SARAM)

– H0: 1 blocco di 8K × 16 SARAM

– M0 e M1: 2 blocchi da 1K × 16 ciascuno di SARAM

• ROM di avvio (4K × 16)

– Con modalità di avvio software

– Tabelle matematiche standard

• Interfaccia esterna (F2812)

– Oltre 1 M × 16 di memoria totale

– Stati di attesa programmabili

– Temporizzazione stroboscopica di lettura/scrittura programmabile

– Tre selezioni di chip individuali

• Endianità: Little endian

• Controllo dell'orologio e del sistema

– Oscillatore on-chip

– Modulo timer watchdog

• Tre interruzioni esterne

• Blocco di espansione dell'interruzione periferica (PIE) chesupporta 45 interrupt periferici

• Tre timer CPU a 32 bit

• Chiave/blocco di sicurezza a 128 bit

– Protegge flash/OTP e L0/L1 SARAM

– Impedisce il reverse engineering del firmware

• Periferiche di controllo motore

– Due Event Manager (EVA, EVB)

– Compatibile con dispositivi 240xA

• Periferiche per porta seriale

– Interfaccia periferica seriale (SPI)

– Due interfacce di comunicazione seriale (SCI),UART standard

– Rete di controllo area avanzata (eCAN)

– Porta seriale multicanale con buffer (McBSP)

• ADC a 12 bit, 16 canali

– Multiplexer di ingresso 2 × 8 canali

– Due Sample-and-Hold

– Conversioni singole/simultanee

– Velocità di conversione rapida: 80 ns/12,5 MSPS

• Fino a 56 pin GPIO (General-Purpose I/O)

• Funzionalità di emulazione avanzate

– Funzioni di analisi e di breakpoint

– Debug in tempo reale tramite hardware

• Gli strumenti di sviluppo includono

– Compilatore/assembler/linker ANSI C/C++

– IDE Code Composer Studio™

– DSP/BIOS™

– Controllori di scansione JTAG

• Standard IEEE 1149.1-1990 Standard IEEEPorta di accesso di prova e Boundary-ScanArchitettura

• Modalità a basso consumo e risparmio energetico

– Modalità IDLE, STANDBY, HALT supportate

– Disabilitare i singoli orologi periferici

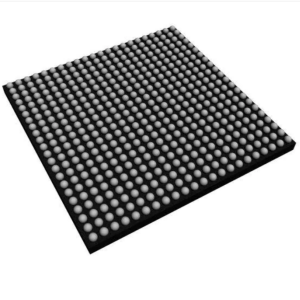

• Opzioni del pacchetto

– MicroStar BGA™ a 179 sfere con memoria esternainterfaccia (GHH, ZHH) (F2812)

– Quad Flatpack a basso profilo a 176 pin (LQFP) coninterfaccia di memoria esterna (PGF) (F2812)

– LQFP a 128 pin senza memoria esternainterfaccia (PBK) (F2810, F2811)

• Opzioni di temperatura

– A: da –40°C a 85°C (GHH, ZHH, PGF, PBK)

– S: da –40°C a 125°C (GHH, ZHH, PGF, PBK)

– Q: da –40°C a 125°C (PGF, PBK)(Qualifica AEC-Q100 per l'automotive

applicazioni)

• Sistemi avanzati di assistenza alla guida (ADAS)

• Automazione degli edifici

• Punto vendita elettronico

• Veicolo elettrico/Veicolo elettrico ibrido (EV/HEV)gruppo propulsore

• Automazione di fabbrica

• Infrastruttura di rete

• Trasporto industriale

• Medicina, assistenza sanitaria e fitness

• Azionamenti motore

• Erogazione di potenza

• Infrastruttura per le telecomunicazioni

• Test e misurazione