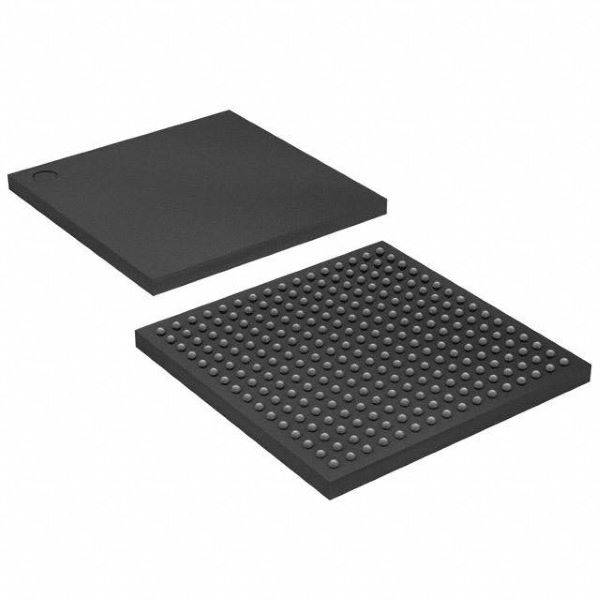

XC6SLX25-2FTG256C FPGA – Field Programmable Gate Array Al momento la fabbrica non accetta ordini per questo prodotto.

♠ Descrizione del prodotto

| Attributo del prodotto | Valore dell'attributo |

| Produttore: | Xilinx |

| Categoria di prodotto: | FPGA - Array di porte programmabili sul campo |

| Direttiva RoHS: | Dettagli |

| Serie: | XC6SLX25 |

| Numero di elementi logici: | 24051 LE |

| Numero di I/O: | 186 I/O |

| Tensione di alimentazione - Min: | 1,14 V |

| Tensione di alimentazione - Max: | 1,26 V |

| Temperatura minima di esercizio: | 0 gradi Celsius |

| Temperatura massima di esercizio: | + 85 °C |

| Velocità dati: | - |

| Numero di ricetrasmettitori: | - |

| Stile di montaggio: | SMD/SMT |

| Confezione/custodia: | FBGA-256 |

| Marca: | Xilinx |

| RAM distribuita: | 229 kbit |

| RAM a blocchi incorporata - EBR: | 936 kbit |

| Frequenza operativa massima: | 1080 MHz |

| Sensibile all'umidità: | SÌ |

| Numero di blocchi di array logici - LAB: | 1879 LAB |

| Tensione di alimentazione operativa: | 1,2 V |

| Tipo di prodotto: | FPGA - Array di porte programmabili sul campo |

| Quantità confezione di fabbrica: | 1 |

| Sottocategoria: | Circuiti integrati logici programmabili |

| Nome commerciale: | spartano |

| Peso unitario: | 21.576 grammi |

♠ Panoramica della famiglia Spartan-6

La famiglia Spartan®-6 offre funzionalità di integrazione di sistema all'avanguardia con il costo totale più basso per applicazioni ad alto volume. La famiglia, composta da tredici componenti, offre densità estese da 3.840 a 147.443 celle logiche, con un consumo energetico dimezzato rispetto alle precedenti famiglie Spartan e una connettività più rapida e completa. Basata su una tecnologia di processo in rame a basso consumo da 45 nm, che offre un equilibrio ottimale tra costi, consumi e prestazioni, la famiglia Spartan-6 offre una nuova e più efficiente logica LUT (Look-Up Table) a doppio registro e 6 ingressi e un'ampia selezione di blocchi integrati a livello di sistema. Queste includono RAM a blocchi da 18 Kb (2 x 9 Kb), slice DSP48A1 di seconda generazione, controller di memoria SDRAM, blocchi di gestione del clock in modalità mista migliorati, tecnologia SelectIO™, blocchi transceiver seriali ad alta velocità con ottimizzazione del consumo energetico, blocchi Endpoint compatibili con PCI Express®, modalità avanzate di gestione dell'alimentazione a livello di sistema, opzioni di configurazione con rilevamento automatico e sicurezza IP avanzata con protezione AES e Device DNA. Queste funzionalità offrono un'alternativa programmabile a basso costo ai prodotti ASIC personalizzati con una facilità d'uso senza precedenti. Gli FPGA Spartan-6 offrono la soluzione migliore per progetti logici ad alto volume, progetti DSP orientati al consumatore e applicazioni embedded sensibili ai costi. Gli FPGA Spartan-6 costituiscono la base in silicio programmabile per le Targeted Design Platform (TPP) che forniscono componenti software e hardware integrati che consentono ai progettisti di concentrarsi sull'innovazione fin dall'inizio del ciclo di sviluppo.

• Famiglia Spartan-6:

• Spartan-6 LX FPGA: logica ottimizzata

• Spartan-6 LXT FPGA: connettività seriale ad alta velocità

• Progettato per costi contenuti

• Blocchi integrati multipli ed efficienti

• Selezione ottimizzata degli standard I/O

• Tamponi sfalsati

• Confezioni in plastica ad alto volume con saldatura a filo

• Bassa potenza statica e dinamica

• Processo a 45 nm ottimizzato per costi e bassi consumi

• Modalità di sospensione per zero consumo energetico

• La modalità di sospensione mantiene lo stato e la configurazione con riattivazione multi-pin e miglioramento del controllo

• Tensione del core a bassa potenza pari a 1,0 V (solo FPGA LX, -1L)

• Tensione del core ad alte prestazioni da 1,2 V (FPGA LX e LXT, gradi di velocità -2, -3 e -3N)

• Banchi di interfaccia SelectIO™ multi-tensione e multi-standard

• Velocità di trasferimento dati fino a 1.080 Mb/s per I/O differenziale

• Uscita selezionabile, fino a 24 mA per pin

• Standard e protocolli da 3,3 V a 1,2 VI/O

• Interfacce di memoria HSTL e SSTL a basso costo

• Conformità hot swap

• Velocità di risposta I/O regolabili per migliorare l'integrità del segnale

• Transceiver seriali GTP ad alta velocità negli FPGA LXT

• Fino a 3,2 Gb/s

• Interfacce ad alta velocità tra cui: Serial ATA, Aurora, 1G Ethernet, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort e XAUI

• Blocco endpoint integrato per progetti PCI Express (LXT)

• Supporto della tecnologia PCI® a basso costo compatibile con le specifiche a 33 MHz, 32 e 64 bit.

• Efficienti slice DSP48A1

• Aritmetica ad alte prestazioni ed elaborazione del segnale

• Moltiplicatore veloce 18 x 18 e accumulatore a 48 bit

• Capacità di pipeline e cascading

• Pre-additivo per facilitare l'applicazione del filtro

• Blocchi del controller di memoria integrato

• Supporto DDR, DDR2, DDR3 e LPDDR

• Velocità di trasmissione dati fino a 800 Mb/s (larghezza di banda di picco di 12,8 Gb/s)

• Struttura bus multiporta con FIFO indipendente per ridurre i problemi di tempistica di progettazione

• Risorse logiche abbondanti con capacità logica aumentata

• Supporto opzionale per registro a scorrimento o RAM distribuita

• Le efficienti LUT a 6 ingressi migliorano le prestazioni e riducono al minimo il consumo energetico

• LUT con doppi flip-flop per applicazioni incentrate sulla pipeline

• RAM a blocchi con un'ampia gamma di granularità

• RAM a blocchi veloci con abilitazione alla scrittura di byte

• Blocchi da 18 Kb che possono essere opzionalmente programmati come due blocchi RAM indipendenti da 9 Kb

• Clock Management Tile (CMT) per prestazioni migliorate

• Clocking flessibile e a basso rumore

• I gestori di clock digitali (DCM) eliminano lo skew del clock e la distorsione del ciclo di lavoro

• Loop ad aggancio di fase (PLL) per clock a basso jitter

• Sintesi di frequenza con moltiplicazione, divisione e sfasamento simultanei

• Sedici reti di clock globali a bassa distorsione

• Configurazione semplificata, supporta standard a basso costo

• Configurazione di rilevamento automatico a 2 pin

• Ampio supporto SPI di terze parti (fino a x4) e flash NOR

• Piattaforma Xilinx Flash ricca di funzionalità con JTAG

• Supporto MultiBoot per l'aggiornamento remoto con più flussi di bit, utilizzando la protezione watchdog

• Maggiore sicurezza per la protezione del design

• Identificatore DNA univoco del dispositivo per l'autenticazione del design

• Crittografia bitstream AES nei dispositivi più grandi

• Elaborazione integrata più rapida con il processore soft MicroBlaze™ migliorato e a basso costo

• Progetti IP e di riferimento leader del settore