Microprocessori P1020NXN2HFB – MPU 800/400/667 ET NE r1.1

♠ Descrizione del prodotto

| Attributo del prodotto | Valore dell'attributo |

| Produttore: | NXP |

| Categoria di prodotto: | Microprocessori - MPU |

| Direttiva RoHS: | Dettagli |

| Stile di montaggio: | SMD/SMT |

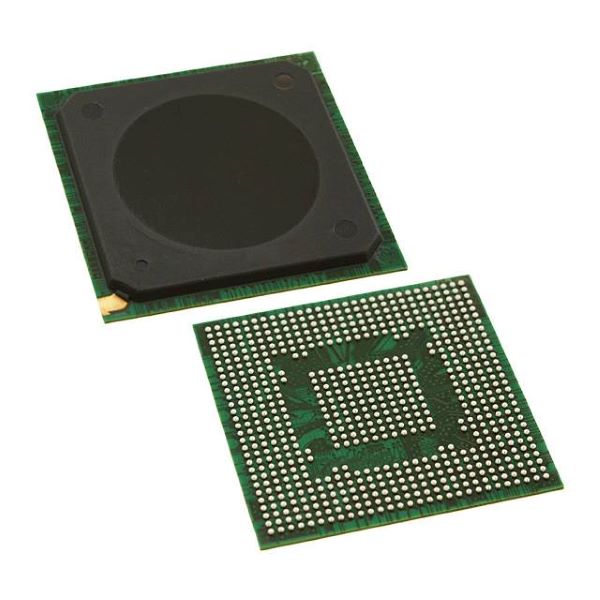

| Confezione/custodia: | TEPBGA-689 |

| Serie: | P1020 |

| Nucleo: | e500 |

| Numero di core: | 2 Nuclei |

| Larghezza del bus dati: | 32 bit |

| Frequenza di clock massima: | 800 MHz |

| Memoria istruzioni cache L1: | 2 x 32 kB |

| Memoria dati cache L1: | 2 x 32 kB |

| Tensione di alimentazione operativa: | 1 V |

| Temperatura minima di esercizio: | - 40 °C |

| Temperatura massima di esercizio: | + 125 °C |

| Confezione: | Vassoio |

| Marca: | NXP Semiconduttori |

| Tensione I/O: | 1,5 V, 1,8 V, 2,5 V, 3,3 V |

| Tipo di istruzione: | Virgola mobile |

| Tipo di interfaccia: | Ethernet, I2C, PCIe, SPI, UART, USB |

| Istruzioni cache L2 / Memoria dati: | 256 kB |

| Tipo di memoria: | Cache L1/L2 |

| Sensibile all'umidità: | SÌ |

| Numero di I/O: | 16 I/O |

| Serie di processori: | QoIQ |

| Tipo di prodotto: | Microprocessori - MPU |

| Quantità confezione di fabbrica: | 27 |

| Sottocategoria: | Microprocessori - MPU |

| Nome commerciale: | QoIQ |

| Timer di controllo: | Nessun timer di controllo |

| Alias del numero di parte: | 935310441557 |

| Peso unitario: | 5,247 g |

• Due core ad alte prestazioni a 32 bit, basati sulla tecnologia Power Architecture®:

– Indirizzamento fisico a 36 bit

– Supporto per calcoli in virgola mobile a doppia precisione

– Cache di istruzioni L1 da 32 Kbyte e cache di dati L1 da 32 Kbyte per ogni core

– Frequenza di clock da 533 MHz a 800 MHz

• Cache L2 da 256 Kbyte con ECC. Configurabile anche come SRAM e memoria di stashing.

• Tre controller Ethernet a tre velocità potenziati da 10/100/1000 Mbps (eTSEC)

– Accelerazione TCP/IP, qualità del servizio e capacità di classificazione

– Supporto IEEE® 1588

– Controllo del flusso senza perdite

– MII, RMII, RGMII, SGMII

• Interfacce ad alta velocità che supportano varie opzioni di multiplexing:

– Quattro SerDes fino a 2,5 GHz/corsia multiplexati sui controller

– Due interfacce PCI Express

– Due interfacce SGMII

• Controller USB ad alta velocità (USB 2.0)

– Supporto host e dispositivo

– Interfaccia del controller host migliorata (EHCI)

– Interfaccia ULPI a PHY

• Controller host digitale sicuro migliorato (SD/MMC)

• Interfaccia periferica seriale avanzata (eSPI)

• Motore di sicurezza integrato

– Il supporto del protocollo include ARC4, 3DES, AES, RSA/ECC, RNG, SSL/TLS a passaggio singolo

– Accelerazione XOR

• Controller di memoria SDRAM DDR2/DDR3 a 32 bit con supporto ECC

• Controllore di interrupt programmabile (PIC) conforme allo standard OpenPIC

• Un controller DMA a quattro canali

• Due controller I2C, DUART, timer

• Controller bus locale avanzato (eLBC)

• TDM

• 16 segnali I/O di uso generale

• Intervallo di temperatura di giunzione operativa (Tj): 0–125°C e da –40°C a 125°C (specifiche industriali)

• WB-TePBGA II da 31 × 31 mm e 689 pin (BGA in plastica con temperatura di saldatura migliorata)