Microcontrollori SPC5675KFF0MMS2 a 32 bit MCU 2MFlash 512KSRAM EBI

♠ Descrizione del prodotto

| Attributo del prodotto | Valore dell'attributo |

| Produttore: | NXP |

| Categoria di prodotto: | Microcontrollori a 32 bit - MCU |

| Direttiva RoHS: | Dettagli |

| Serie: | MPC5675K |

| Stile di montaggio: | SMD/SMT |

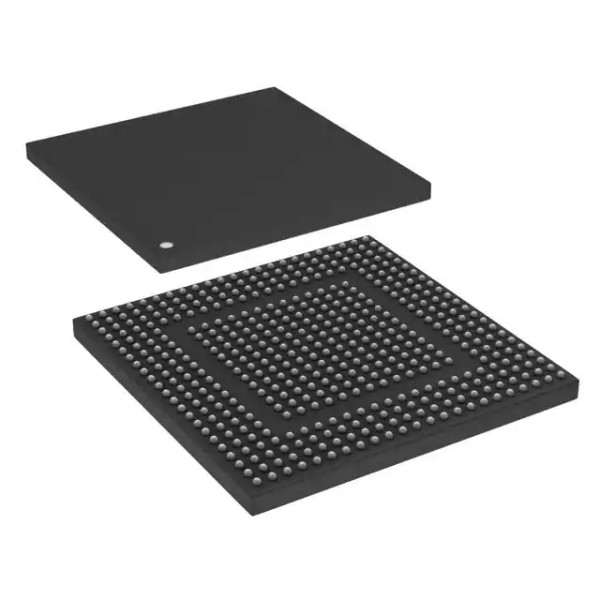

| Confezione/custodia: | BGA-473 |

| Nucleo: | e200z7d |

| Dimensione della memoria del programma: | 2 MB |

| Dimensione RAM dati: | 512 kB |

| Larghezza del bus dati: | 32 bit |

| Risoluzione ADC: | 12 bit |

| Frequenza di clock massima: | 180 MHz |

| Tensione di alimentazione - Min: | 1,8 V |

| Tensione di alimentazione - Max: | 3,3 V |

| Temperatura minima di esercizio: | - 40 °C |

| Temperatura massima di esercizio: | + 125 °C |

| Qualificazione: | AEC-Q100 |

| Confezione: | Vassoio |

| Tensione di alimentazione analogica: | 3,3 V/5 V |

| Marca: | NXP Semiconduttori |

| Tipo di RAM dati: | SRAM |

| Tensione I/O: | 3,3 V |

| Sensibile all'umidità: | SÌ |

| Serie di processori: | MPC567xK |

| Prodotto: | MCU |

| Tipo di prodotto: | Microcontrollori a 32 bit - MCU |

| Tipo di memoria del programma: | Flash |

| Quantità confezione di fabbrica: | 420 |

| Sottocategoria: | Microcontrollori - MCU |

| Timer di controllo: | Timer di controllo |

| Alias del numero di parte: | 935310927557 |

| Peso unitario: | 0,057260 once |

♠ Microcontrollore MPC5675K

Il microcontrollore MPC5675K, una soluzione SafeAssure, è unController incorporato a 32 bit progettato per driver avanzatisistemi di assistenza con RADAR, immagini CMOS, LIDARe sensori a ultrasuoni e controllo multiplo del motore trifaseapplicazioni come nei veicoli elettrici ibridi (HEV) inapplicazioni automobilistiche e industriali ad alte temperature.

Membro della famiglia MPC5500/5600 di NXP Semiconductor,contiene l'architettura di alimentazione conforme al Libro Enucleo tecnologico con codifica a lunghezza variabile (VLE). Questoil core è conforme all'architettura Power incorporatacategoria, ed è compatibile al 100% con la modalità utentearchitettura originale del set di istruzioni per l'utente del Power PC™ (UISA).Offre prestazioni di sistema fino a quattro volte superiori a quelle del suoPredecessore MPC5561, offrendoti al contempo l'affidabilità efamiliarità con la comprovata tecnologia Power Architecture.

Una suite completa di hardware e softwaresono disponibili strumenti di sviluppo per semplificare e velocizzareprogettazione del sistema. Il supporto allo sviluppo è disponibile dafornitori leader di strumenti che forniscono compilatori, debugger eambienti di sviluppo di simulazione.

• Processore dual core e200z7d ad alte prestazioni

— CPU con tecnologia Power Architecture a 32 bit

— Frequenza del core fino a 180 MHz

— Nucleo a doppia emissione

— Codifica a lunghezza variabile (VLE)

— Unità di gestione della memoria (MMU) con 64 voci

— Cache di istruzioni da 16 KB e cache di dati da 16 KB

• Memoria disponibile

— Memoria flash di codice fino a 2 MB con ECC

— Memoria flash dati da 64 KB con ECC

— Fino a 512 KB di SRAM on-chip con ECC

• Concetto di sicurezza innovativo SIL3/ASILD: modalità LockStep e protezione fail-safe

— Sfera di replicazione (SoR) per i componenti chiave

— Unità di controllo della ridondanza sulle uscite del SoR collegate a FCCU

— Unità di raccolta e controllo guasti (FCCU)

— Autotest integrato all'avvio per la memoria (MBIST) e la logica (LBIST) attivato dall'hardware

— Autotest integrato all'avvio per ADC e memoria flash

— Timer di controllo replicato con sicurezza migliorata

— Sensore di temperatura del substrato di silicio (die)

— Interruzione non mascherabile (NMI)

— Unità di protezione della memoria (MPU) a 16 regioni

— Unità di monitoraggio dell'orologio (CMU)

— Unità di gestione dell'alimentazione (PMU)

— Unità di controllo di ridondanza ciclica (CRC)

• Modalità parallela disaccoppiata per l'utilizzo ad alte prestazioni dei core replicati

• Interfaccia Nexus Classe 3+

• Interruzioni

— Controller di interrupt a 16 priorità replicato

• GPIO programmabili individualmente come input, output o funzione speciale

• 3 unità eTimer per uso generale (6 canali ciascuna)

• 3 unità FlexPWM con quattro canali a 16 bit per modulo

• Interfacce di comunicazione

— 4 moduli LINFlex

— 3 moduli DSPI con generazione automatica della selezione del chip

— 4 interfacce FlexCAN (2.0B attive) con 32 oggetti messaggio

— Modulo FlexRay (V2.1) con doppio canale, fino a 128 oggetti messaggio e fino a 10 Mbit/s

— Controller Fast Ethernet (FEC)

— 3 I2Moduli C

• Quattro convertitori analogico-digitali (ADC) a 12 bit

— 22 canali di ingresso

— Unità di cross triggering programmabile (CTU) per sincronizzare la conversione ADC con timer e PWM

• Interfaccia bus esterna

• Controller di memoria DDR esterno a 16 bit

• Interfaccia digitale parallela (PDI)

• Caricatore bootstrap CAN/UART su chip

• In grado di funzionare con una singola alimentazione a 3,3 V

— 3.3 Moduli solo V: I/O, oscillatori, memoria flash

— Moduli da 3,3 V o 5 V: ADC, alimentazione al VREG interno

— Intervallo di alimentazione 1,8–3,3 V: DRAM/PDI

• Intervallo di temperatura di giunzione operativa da -40 a 150 °C